# A Virtual Machine Approach for High-level FPGA Programming

## • High-level FPGA programming • Objectives: • enhance the programmability of FPGAs • allow quick prototyping • simulation and acceleration of applications • A virtual machine approach: • **O2B** (*OCaml on board*) https://github.com/jserot/O2B • Macle (*ML accelerator*) https://github.com/lsylvestre/macle • **OCaml:** A high-level programming language (functional, imperative, modular, object-oriented) let main() = print\_int (f 80); let x = 1000 and y = 12000000 in let t\_c = chrono gcd\_c x y in let t\_rtl = chrono gcd x y in **let** t\_par = let src = Array.create (128\*10) x in let dst = Array.create (128\*10) x in chrono (map\_gcd\_by\_100 y) src dst in print\_int (t\_c / t\_rtl); print\_int (t\_c / t\_par); try print\_int (nth 42 [1;2;3;4]) with Failure s -> print\_string s ;; main() ;;

### **6** Preliminary evaluation

- on a small FPGA: 50K logic cells and 1,6 Kbits of on-chip memory with a clock frequency of 50 MHz

- •t\_c / t\_rtl: hardware acceleration of the function gcd versus a C version running on the softcore provides a  $\times$  **30 speedup**. Speedups depend on the nature of the computations. They can be higher than 30.

- •t\_rtl / t\_par: hardware acceleration of map\_gcd\_by\_100 (using a parallel skeletons) provides an extra speedup of almost 100.

- •t\_c / t\_par: resulting speedup of almost 3000.

<sup>1</sup>LIP6, CNRS, Sorbonne Université

<sup>2</sup>Université Clermont Auvergne, CNRS, SIGMA, Institut Pascal

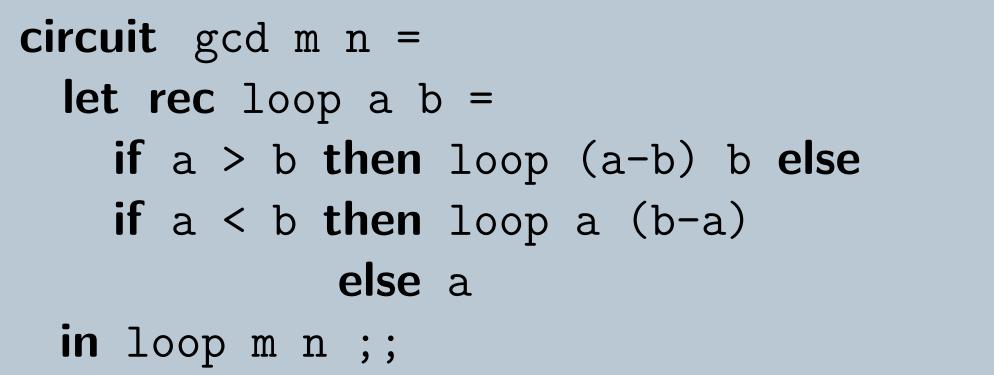

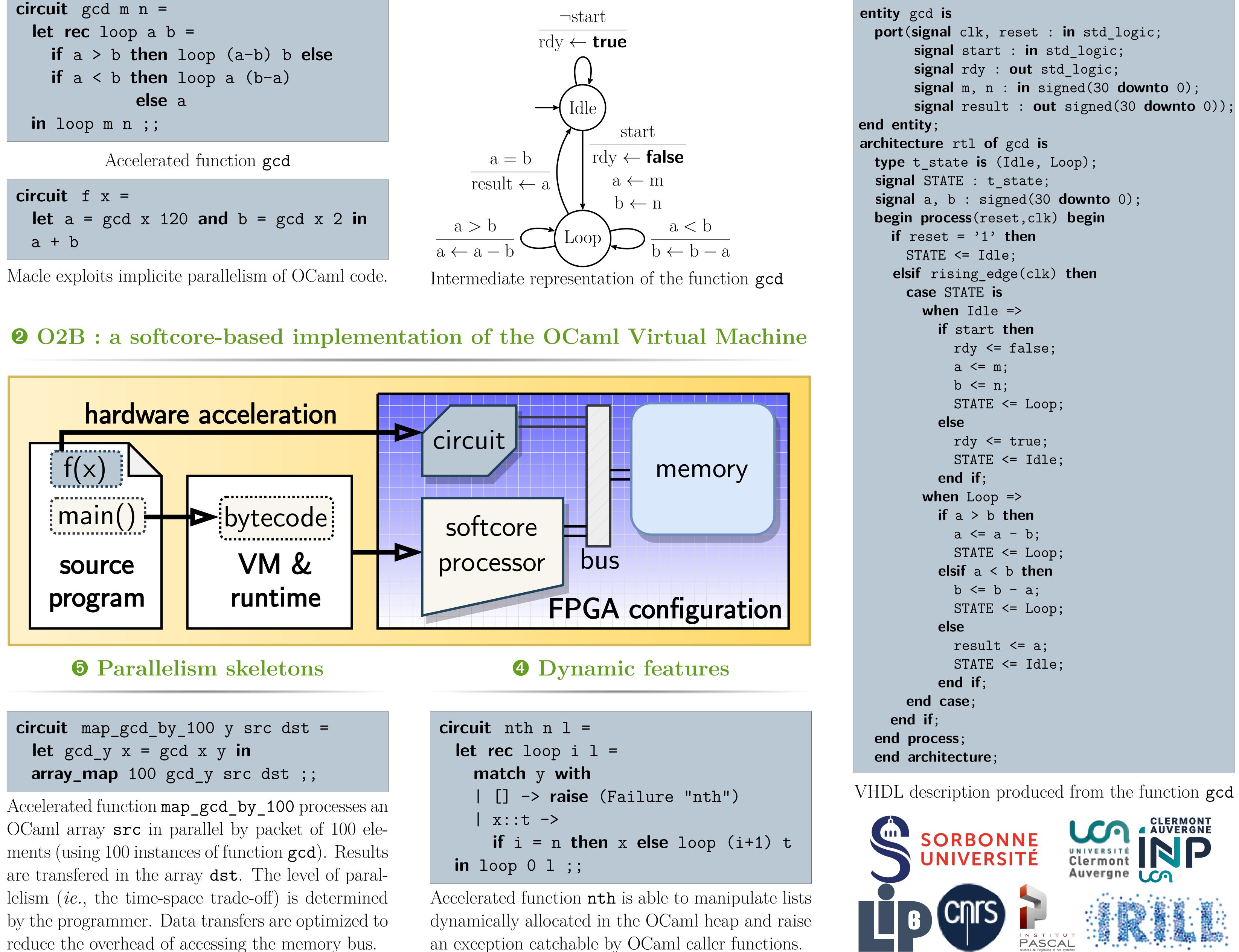

#### **3** Macle : a compiler for a subset of OCaml targeting the register transfer level

```

circuit f x =

a + b

```

reduce the overhead of accessing the memory bus.

Loïc Sylvestre<sup>1</sup> Jocelyn Sérot<sup>2</sup> Emmanuel Chailloux<sup>1</sup>

```

signal result : out signed(30 downto 0));

```